## **HONOR CODE**

- I have not used any online resources during the exam.

- I have not obtained any help either from anyone in the class or outside when completing this exam.

- · No sharing of notes/slides/textbook between students.

- CANVAS ANSWERS MAY BE LOCKED AFTER 1ST TRY.

## **Questions Sheet.**

Read all of the following information before starting the exam:

- For each question fill out the appropriate choice or write text on page. Also type clearly on in the exam on the appropriate text.

- IF THE MULTIPLE CHOICE ANSWER IS WRONG WE WILL MARK THE ANSWER WRONG. IF THE MULTIPLE-CHOICE ANSWER IS CORRECT, WE WILL READ THE WRITTEN PORTION.

- 1 pt Qs (0 or 1). 2 or 3pt Qs (if no explaination only 1 pt.)

- Show all work, clearly and in order, if you want to get full credit.

- We reserve the right to take off points if we cannot see how you logically got to the answer (even if your final answer is correct). 1 or 2 sentences atmost.

- I will take points off for rambling and for incorrect or irrelevant statements.

- HONOR CODE

- · Questions Sheet.

- Section A Virtual Memory 15 points. Canvas Q1-Q28

- Common questions. Canvas Q1-Q2

- For the virtual address 0x15957 answer the following Canvas Q3-Q12. All in hex. (0.5 pt each)

- For the virtual address 0x2ee19 answer the following. Canvas Q13-Q22. All in hex (0.5 pt each)

- For the virtual address 0x1a344 answer the following. All in hex (Canvas: 23-28) (0.5 pt each)

- B. Easy. RISCV Blackbox. [10 Points]

- Answer questions below for the code shown.

- 29. \_\_\_\_ bytes are stored to memory? [1]

- 30. The string result is "\_\_\_\_\_" ? [1]

- Answer questions below for the code shown.

- 31. \_\_\_\_ bytes are stored to memory? [1]

- 32. The string result is "\_\_\_\_\_" ? [2]

- Answer questions below for the code shown.

- o 33. \_\_\_\_ bytes are stored to memory? [2]

- 34. The string result is \_\_\_\_\_? [3]

- C. Lets Cache I (14pts)

- 35. The hit ratio of loop 1 for Cache A is ----? (1 pts)

- 36. The hit ratio of loop 1 for Cache B is ----? (1 pts)

- 37. The hit ratio of loop 2 for Cache A is ---- (assume loop 1 has already run) ? (1 pts)

- 38. The hit ratio of loop 2 for Cache B is ---- (assume loop 1 has already run) ? (1 pts)

- 39. The hit ratio of loop 3 for Cache A is ---- (assume loop 1 and 2 has already run) ? (2 pts)

- 40. The hit ratio of loop 3 for Cache B is ---- (assume loop 1 and 2 has already run)? (2 pts)

- 41. What is the hit ratio if loop 3 changes to the one below (on Cache A)? (2 pts)

- 42. What is the hit ratio if loop 3 is same as Q41 for lines 7-10. (on Cache B) ? (2 pts)

- 43. What is hit ratio for the code below. Assume Cache B? (2 pts)

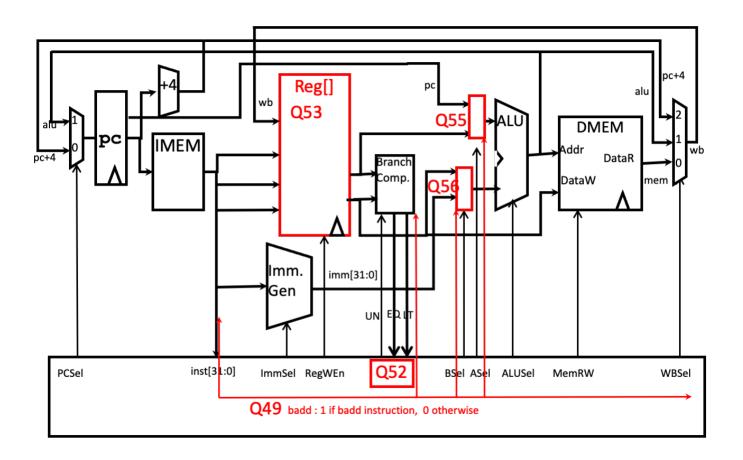

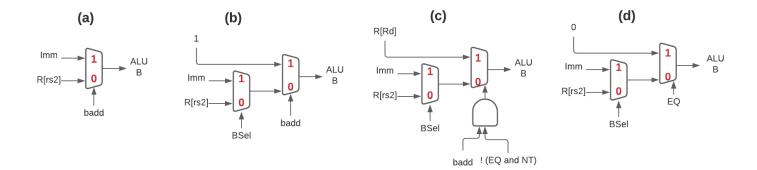

- D. RISC-V Single Cycle Datapath [15 points]

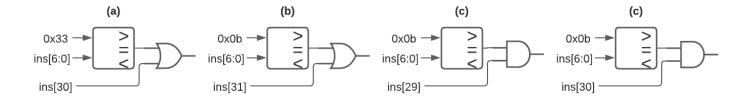

- 44. What is the logic for badd signal? (1)

- 45. \_\_\_\_ is the number of registers badd needs to access in a single cycle ? (1)

- 46. What is the RegWen signal for badd? (1)

- 47. What is the comparison logic we are interested in ? (2)

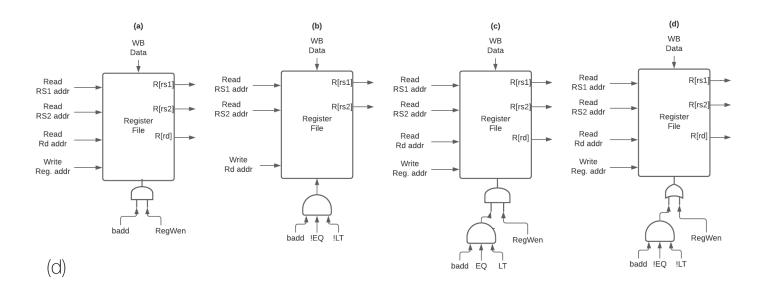

- 48. Consider the following modifications to the Reg[] register file. (2)

- 49. What is ASel and BSel (2)

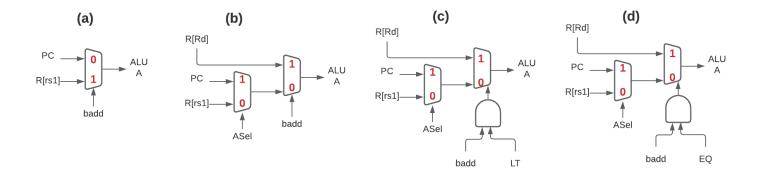

- 50. What are the changes to mux-A? (2)

- 51. What are the changes to mux-B? (2)

- 52. The WBsel select is \_\_\_\_\_ ? (2)

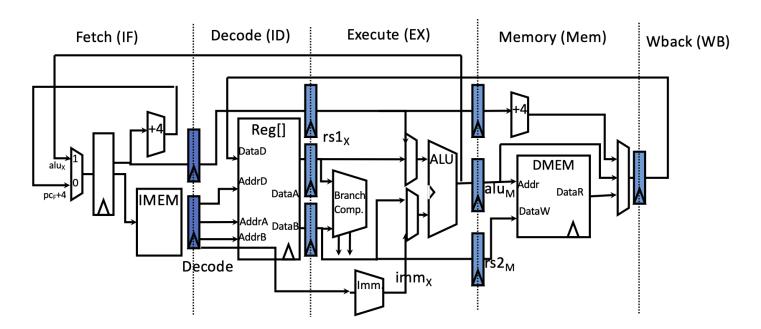

- F. RISC-V Pipeline 17 points.

- Part I

- 53. What hazards existing between line 3 and 4? (1) • 54. What hazards existing between line 4 and 5? (1) • 55. What is the instruction in IF stage t = 6 ? line \_\_\_\_ (1) • 56. What is the instruction in IF stage of t = 7? line \_\_\_\_ (1) • 57. How many cycles does this program take to complete ? \_\_\_\_ (2) Part 2. • 58. What is the instruction in IF stage t = 6? line \_\_\_\_\_(1) • 59. What is the instruction in IF stage of t = 7? line \_\_\_\_\_ (1) 60. How many cycles does this program take to complete ? \_\_\_\_\_\_\_(2) o Part 3. • 61. What is the instruction in IF stage t = 6? (1) • 62. What is the instruction in IF stage of t = 7? (1) o Part 4. • 64. What is the instruction in IF stage t = 6? (1) 65. How many cycles does this program take to complete ? \_\_\_\_\_\_\_(2)

- F. Pipeline CPU.

- o 66. Assuming that this CPU is NOT Pipelined (i.e. it is a singlecycle CPU), what is the

- 67. Assuming that this CPU is Pipelined, what is the

## Section A Virtual Memory 15 points. Canvas Q1-Q28

Refer slide deck L21-VM-III Week 8 if you need to.

The chart below shows how memory accesses are treated in a system. The table below describes the parameters int he memory system.

Please use the data below to answer question groups Q1,Q2,Q3,Q4 on canvas.

CAUTION 1: When converting from binary to hex you can always pad the MSB e.g., 10 1010 (6 bit field) in hex is 0010 1010 (2 0s padded in MSB) is  $0 \times 2a$ .

always use lower case and prefix 0x for hex.

Correct: 0xabcdef Incorrect: 0xABCDEF

| Parameter             | Value     |

|-----------------------|-----------|

| Physical address bits | 18        |

| Size of page          | 64 bytes  |

| Virtual address bits  | 18        |

|                       |           |

| TLB Sets              | 8         |

| TLB Ways              | 2         |

|                       |           |

| Cache size            | 256 bytes |

| Cache Sets            | 16        |

| Cache Ways            | 2         |

- VPN Virtual page number

- Index (Set index of cache or TLB)

- PPN Physical page number

- INVALID. TLB entry is invalid

- TLB-T (TLB Tag)

| Way 0 | TLB-T   | PPN   |

|-------|---------|-------|

| Set 0 | [0x1cb] | 0x958 |

| Set 1 | [0x1be] |       |

| Set 2 | [0xa4]  | 0xe76 |

| Set 3 | [0x74]  |       |

| Set 4 | [0x11d] | 0x2b5 |

| Set 5 | [0xbc]  | 0xa36 |

| Set 6 | [0x1fb] |       |

| Set 7 | [0xf1]  | 0xfea |

| Way 0 | TLB-T   | PPN   |

|-------|---------|-------|

| Set 0 | [0x177] | 0x47b |

| Set 1 | [0x24]  |       |

| Set 2 | [0x12]  | 0x84a |

| Set 3 | [0x16c] |       |

| Set 4 | [0x192] | 0xe76 |

| Set 5 | [0xd1]  |       |

| Set 6 | [0xab]  | 0xec3 |

| Set 7 | [0xc6]  |       |

## Page Table (Partial)

${\tt CAUTION:\ Only\ partial\ table\ relevant\ to\ the\ questions\ are\ shown.}$

| VPN   | PPN   | Valid |

|-------|-------|-------|

| 0xbb8 | 0x47b | 1     |

| 0xe58 | 0x958 | 1     |

| 0x522 | e76   | 1     |

| 0xdf1 |       | 0     |

| 0xfde |       | 0     |

| 0x78f | fea   | 1     |

| 0x383 | 0xa3  | 1     |

| 0x68d |       | 0     |

| 0x565 | 0x636 | 1     |

Way 0

| Set 0  | [0x322] | 0x13 | 0xc8 | 0xce | 0xc6 | 0x76 | 0x7c | 0xde | 0xf3 |

|--------|---------|------|------|------|------|------|------|------|------|

| Set 1  | [0x45a] | 0xbc | 0x0f | 0xd8 | 0x93 | 0xe7 | 0x69 | 0xea | 0xb1 |

| Set 2  | [0x6f6] | 0x56 | 0xf3 | 0x3d | 0xd6 | 0x7b | 0x2c | 0x98 | 0x34 |

| Set 3  | [0x276] | 0xf3 | 0x8c | 0x94 | 0x8d | 0xaf | 0x5c | 0x02 | 0x3b |

| Set 4  | [0x23c] | 0x3a | 0x09 | 0x3c | 0x3b | 0x35 | 0x3f | 0x85 | 0x1e |

| Set 5  | [0x425] | 0x19 | 0x65 | 0xaf | 0x3e | 0xb4 | 0x8a | 0x8a | 0xcf |

| Set 6  | [0x62e] | 0x88 | 0x87 | 0xad | 0x73 | 0xac | 0x70 | 0xeb | 0x77 |

| Set 7  | [0x4ac] | 0x0c | 0x02 | 0x16 | 0xfe | 0x7b | 0x34 | 0xd6 | 0x91 |

| Set 8  | [0x761] | 0xc9 | 0x97 | 0x01 | 0x6d | 0xea | 0x55 | 0x59 | 0x73 |

| Set 9  | [0x242] | 0xe2 | 0x55 | 0x38 | 0xd0 | 0x84 | 0x6c | 0x16 | 0x5b |

| Set 10 | [0x494] | 0x76 | 0x78 | 0x19 | 0x6b | 0xb6 | 0xf3 | 0xa4 | 0xfb |

| Set 11 | [0x23d] | 0xf5 | 0xac | 0x7f | 0xf5 | 0x1f | 0xb8 | 0x03 | 0x20 |

| Set 12 | [0x7b9] | 0x11 | 0x9a | 0xd4 | 0x8d | 0x85 | 0xe8 | 0xb3 | 0xb1 |

| Set 13 | [0x15a] | 0x4e | 0xaa | 0x51 | 0x0f | 0x61 | 0xc3 | 0x8f | 0x0e |

| Set 14 | [0x739] | 0x77 | 0x71 | 0x3b | 0xb8 | 0xa7 | 0x70 | 0x18 | 0x15 |

| Set 15 | [0x627] | 0x7f | 0x65 | 0xe0 | 0x34 | 0x1a | 0x90 | 0xb5 | 0x19 |

| Way 1  | Tag     | 0    | 1    | 2    | 3    | 4    | 5    | 6    | 7    |

| Set 0  | [0x7f5] | 0x11 | 0xbf | 0xe8 | 0x3e | 0xad | 0x26 | 0x2e | 0xaa |

| Set 1  | [0x73b] | 0xe3 | 0x08 | 0x0b | 0x3a | 0xc6 | 0x98 | 0x67 | 0x17 |

| Set 2  | [0x31b] | 0x39 | 0x16 | 0x2e | 0xbc | 0xde | 0x90 | 0xb5 | 0x61 |

| Set 3  | [0x755] | 0x2b | 0x39 | 0x46 | 0xf5 | 0x95 | 0xb7 | 0x43 | 0x6d |

| Set 4  | [0x627] | 0x51 | 0x8f | 0x28 | 0xb4 | 0x1d | 0xac | 0x8c | 0x3d |

| Set 5  | [0x2af] | 0xf5 | 0x49 | 0x67 | 0x1d | 0xcb | 0x75 | 0x8e | 0x05 |

|        |         |      |      |      |      |      |      |      |      |

Tag

| Way 1  | Tag     | 0    | 1    | 2    | 3    | 4    | 5    | 6    | 7    |

|--------|---------|------|------|------|------|------|------|------|------|

| Set 6  | [0xf2]  | 0xc1 | 0xcd | 0x99 | 0xce | 0x27 | 0xb1 | 0x9b | 0xaf |

| Set 7  | [0x236] | 0xbb | 0xe4 | 0xda | 0xcd | 0x43 | 0xa6 | 0xa0 | 0x11 |

| Set 8  | [0x1c1] | 0x02 | 0x29 | 0xe3 | 0x33 | 0xa9 | 0x24 | 0x89 | 0x1e |

| Set 9  | [0x335] | 0x32 | 0x44 | 0x68 | 0x76 | 0x7b | 0xfb | 0x7d | 0xc9 |

| Set 10 | [0x64]  | 0x3c | 0x84 | 0x70 | 0x27 | 0x98 | 0x88 | 0x96 | 0x73 |

| Set 11 | [0x51]  | 0x50 | 0x82 | 0x6c | 0xda | 0x93 | 0x3a | 0x77 | 0x8b |

| Set 12 | [0x56f] | 0x9c | 0xd1 | 0xc7 | 0xba | 0x62 | 0xde | 0x1e | 0x37 |

| Set 13 | [0x654] | 0xd5 | 0x9c | 0x66 | 0x8f | 0x95 | 0xa6 | 0x3f | 0x4c |

| Set 14 | [0x1e4] | 0xc9 | 0x96 | 0xb0 | 0x3b | 0xfb | 0x76 | 0xa3 | 0x77 |

| Set 15 | [0x5d8] | 0xb3 | 0x4f | 0x91 | 0xe9 | 0x6e | 0xa5 | 0x91 | 0x8a |

# Common questions. Canvas Q1-Q2

|   | 1. | How | many | bits | is the | VPN. | decimal | (1pt) | ? |

|---|----|-----|------|------|--------|------|---------|-------|---|

| 1 | 2  |     |      |      |        |      |         |       |   |

|   | 2. | How | many | bits | is the | PPN. | decimal | (1pt) | ? |

| 1 | 2  |     |      |      |        |      |         |       |   |

# For the virtual address 0x15957 answer the following Canvas Q3-Q12. All in hex. (0.5 pt each)

· What is the VPN

101 01100 101 010000

### 0x565

• What is the TLB tag.

### 0xac

• Is it a TLB hit or miss

### Miss

• Is it a page fault

### No

. What is the PPN?

### PPN:0x636

PPA: 0x18d97

• what is the cache tag?

#### 0x31b

· what is the cache index

### 0x2

What is the byte offset

· Is it a cache hit or miss

Hit

• What is the data byte

0x61

# For the virtual address 0x2ee19 answer the following. Canvas Q13-Q22. All in hex (0.5 pt each)

What is the VPN

### 0xbb8

What is the TLB tag.

### 0x177

· Is it a TLB hit or miss

Hit

• Is it a page fault

No

• What is the PPN?

### 0x47b

• what is the cache tag?

### 0x23d

· what is the cache index

#### 0xb

• What is the byte offset

### 0x1

· Is it a cache hit or miss

• What is the data byte

0xac

# For the virtual address 0x1a344 answer the following. All in hex (Canvas: 23-28) (0.5 pt each)

00110 1000 1101 000100

- What is the VPN 0x68d

- What is the TLB tag. 0xd1

- Is it a TLB hit or miss hit

- Is it a page fault yes

- What is the PPN ? N/A

- Is it a cache hit?No

## B. Easy. RISCV Blackbox. [10 Points]

WARNING: FOR THIS QUESTION MAKE SURE YOU WRITE YOUR CORRECT ANSWER AT THE BEGINNING.

ALSO WRITE ONE/TWO SENTENCES REASONING YOUR ANSWER. OTHERWISE WE WILL SIMPLY ZERO IT OUT.

Assume we have two arrays input and result.

a0=message, a1=result . Answer questions below.

```

char *message = "ABCDE"

char result[20];

```

### Answer questions below for the code shown.

```

1 | lbu s0 0(a0)

2 | slli s1 s0 8

3 | add s1 s1 s0

4 | sh s1 0(a1)

```

29. \_\_\_\_ bytes are stored to memory? [1]

2

30. The string result is "\_\_\_\_\_" ? [1]

AA

### Answer questions below for the code shown.

```

1 | BLACKBOX:

2 | 1bu s0 0(a0)

3 | slli s1 s0 8

4 | addi s0 s0 1

5 | add s1 s1 s0

6 | slli s2 s1 16

7 | addi s2 s2 s0

8 | sw s2 0(a1)

```

31. \_\_\_\_ bytes are stored to memory? [1]

4

32. The string result is "\_\_\_\_\_" ? [2]

### Answer questions below for the code shown.

### 33. \_\_\_\_ bytes are stored to memory? [2]

```

_1 | .text

BLACKBOX:

2

lbu s0 0(a0)

beq s0 x0 End

slli s1 s0 8

5

add s1 s1 s0

sh s1 0(a1)

sb s0 2(a1)

addi a0 a0 1

addi a1 a1 3

10

j BLACKBOX

end:

12

sb x0 0(a1)

13

```

16 (5 letters  $\times$  3 + null character)

### 34. The string result is \_\_\_\_\_ ? [3]

"AAABBBCCCDDDEEE"

# C. Lets Cache I (14pts)

Assume we are working in a 4GB physical address space.

We will be studying the behavior of different loops on two different caches.

| Cache-A | Direct-mapped, 4KB, 64 sets         |

|---------|-------------------------------------|

| Cache-B | Set-associate, 4KB, 2 ways, 32 sets |

Both caches use write-back and write-allocate policies.

Hit ratio is written as #Hits:#Accesses

Hit-Miss ratio is: #Hits:#Misses Hit %: #Hits:#Accesses \* 100.

Answer questions below

```

int size = 4096;

// int is 4 bytes

int a[size];

// long long int is 8 bytes

long long int a_long[size];

/* loop 1 */

for (int i = 0; i < size; i++) {

a[i] = i;

}

/* loop 2 */

for (int i = 0; i < size; i++) {

a_{\log[i]} = i;

}

/* loop 3 */

for (int i = 0; i < size/2; i += 1) {

a[(size/2+i] = a[i];

}

```

35. The hit ratio of loop 1 for Cache A is ----? (1 pts)

Write it as Hits:Accesses

15:16

36. The hit ratio of loop 1 for Cache B is ----? (1 pts)

15:16

37. The hit ratio of loop 2 for Cache A is ---- (assume loop 1 has already run) ? (1 pts)

7:8

38. The hit ratio of loop 2 for Cache B is ---- (assume loop 1 has already run) ? (1 pts)

7:8

39. The hit ratio of loop 3 for Cache A is ---- (assume loop 1 and 2 has already run) ? (2 pts)

0

MM

# 40. The hit ratio of loop 3 for Cache B is ---- (assume loop 1 and 2 has already run) ? (2 pts)

15:16

MMHHHH(repeats HH 15 times)

# 41. What is the hit ratio if loop 3 changes to the one below (on Cache A) ? (2 pts)

3/4

МНННМННН

# 42. What is the hit ratio if loop 3 is same as Q41 for lines 7-10. (on Cache B) ? (2 pts)

15:16

1st iteration MHHHMHHH

2nd interation HHHH HHHH

...

5th iteration MHHHMHHHH

43. What is hit ratio for the code below. Assume Cache B? (2 pts)

```

struct int_and_long {

int a_int;

long long int a_long;

};

int size = 4096;

// int is 4 byte aligned

// long long int is 8 byte aligned

/* loop 1 */

for (int i = 0; i < size/2; i += 1) {

s[size-1-i].a_int = s[i].a_int

}</pre>

```

Struct has to add 4 byte padding to a\_int so total size of struct is 16 bytes.

Each cache line in A can hold 4 structs or 4 a\_ints.

3:4 hits. e.g, s[0] and s[4095]

M,M,H,H,H,H,H,H

## D. RISC-V Single Cycle Datapath [15 points]

We wish to introduce a new instruction into our RISC-V datapath.

badd (branch and add). This instruction is a conditional add instruction. The instruction works as follows. The instruction is encoded as follows.

#### Add instruction

|    |     |     |     |    |    | Opcode  |

|----|-----|-----|-----|----|----|---------|

| f7 | rs2 | rs1 | 0x0 | f3 | rd | 0110011 |

### new badd instruction

| 0x10 | rs2 | rs1 | 0x0 | f3 | rd | 0001011 |

|------|-----|-----|-----|----|----|---------|

```

1 | if (R[rs1] > R[rs2]) {

2     R[rd]++

3     } else     {

4          R[rd] = R[rd]

5     }

```

It combines the semantics of branch and R-type instruction.

- Like a branch it performs a comparison.

- If comparison succeeds it increments rd. rd is destination and source.

- If comparison fails, it simply retains the value in R[rd].

- We have a new control signal badd which is 1 if the instruction being decoded is a badd.

Given the single cycle datapath below, select the correct modifications in parts such that the datapath executes correctly for this new instruction (and all other instructions!). You can make the following assumptions:

Caution 2: Pay careful attention to which input line is 1 and which line is 0 in the muxes. Some muxes choose top-most input as 0, some choose bottom-most input as 0

Hint: YOU DO NOT REQUIRE TRUTH TABLES

Try writing down in plain english or reading out the logic to yourself e.g, !(A<=B) is A is not equal to B and A is not LT (less than) B

## 44. What is the logic for badd signal ? (1)

С

ins[6:0] == 0x0b && ins[29] == 0x1

45. \_\_\_\_ is the number of registers badd needs to access in a single cycle ? (1)

3

## 46. What is the RegWen signal for badd ? (1)

### 47. What is the comparison logic we are interested in ? (2)

!(EQ OR LT)

## 48. Consider the following modifications to the Reg[] register file. (2)

Which configuration will allow this instruction to execute correctly without breaking the execution of other instructions in our instruction set?

## 49. What is ASel and BSel (2)

Don't care

## 50. What are the changes to mux-A? (2)

Which configuration will allow this instruction to execute correctly without breaking the execution of other instructions in our instruction set?

В

### 51. What are the changes to mux-B? (2)

Which configuration will allow this instruction to execute correctly without breaking the execution of other instructions in our instruction set?

В

### 52. The WBsel select is \_\_\_\_\_ ? (2)

**ALU**

# F. RISC-V Pipeline 17 points.

Refer slide deck L29-Hazard Week 11 if you need to.

Consider a typical 5-stage (Fetch, Decode, EXecute, Memory, WriteBack) pipeline. Assume pipeline registers exist where the dotted lines are.

### READ RULES BELOW

Forwarding/Bypassing is implemented.

- Branches targets are calculated in the EX stage.

- Branch comparison in the EX stage.

- We can read and write the register in a cycle.

- A stall is the number of extra cycles an instruction wastes cause of a hazard.

- Assume at t=0 instruction addi t1,t1,1 is in IF stage when calculating cycles below.

### Part I

```

if (a0 == 1) {

// Choice 1

} else if (a0 == 2) {

// Choice 2

} else if (a0 == 3) {

// Choice 3

}

```

The assembly code below implements the following

```

_1 | main:

addi a0,zero,1

2

addi t1,t1,1

3

beq a0,t1,choice1

4

addi t1,t1,1

5

beq a0,t1,choice2

6

addi t1,t1,1

7

beq a0,t1,choice3

8

9

choice1: # Jumped into choice 1

10

j end

11

choice2: # Jumped into choice 2.

12

j end

13

choice3:

j end

15

end:

16

addi a0, zero, 10

17

ecall # terminate ecall

```

Use the provided linux numbers in code listing when answering questions below

### 53. What hazards existing between line 3 and 4? (1)

Data

### 54. What hazards existing between line 4 and 5? (1)

line 11: j end

| 55. What is the instruction in IF stage t = 6 ? line (1)                                                |

|---------------------------------------------------------------------------------------------------------|

| only write line number e.g., 2 if instruction is addi a0,zero,1                                         |

| 13: jal zero, end                                                                                       |

| 56. What is the instruction in IF stage of t = 7 ? line (1)                                             |

| 15: jal zero, end                                                                                       |

| 57. How many cycles does this program take to complete ? (2)                                            |

| 16                                                                                                      |

| Part 2.                                                                                                 |

| For questions below assume we have changed line 2 to addi a0, zero, 2 i.e., we are going into choice 2. |

| 58. What is the instruction in IF stage t = 6 ? line (1)                                                |

| line 8:beq a0,t1,choice3                                                                                |

| 59. What is the instruction in IF stage of t = 7 ? line (1)                                             |

| line 13: j end                                                                                          |

| 60. How many cycles does this program take to complete? (2)                                             |

| 18                                                                                                      |

| Part 3.                                                                                                 |

| For questions below assume we have changed line 2 to addi a0, zero, 3 i.e., we are going into choice 3. |

| 61. What is the instruction in IF stage t = 6 ? (1)                                                     |

| line8:beq a0,t1,choice3                                                                                 |

| 62. What is the instruction in IF stage of t = 7 ? (1)                                                  |

20

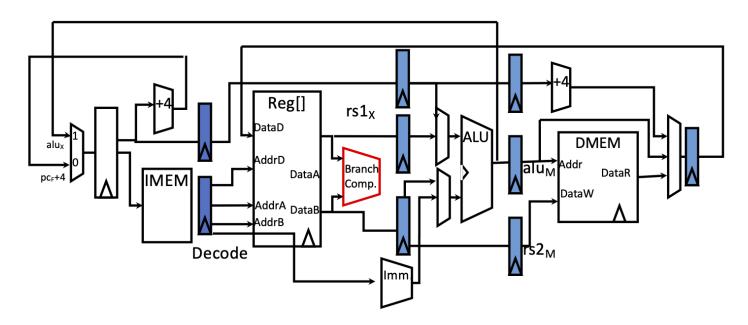

## Part 4.

Now consider the pipeline modification below

- The branch comparison has been moved to the Decode stage

- Note that branch addresses still get resolved only in the EX stage.

- Answer questions below. Hint: Think about data hazards for the branch instruction

## 64. What is the instruction in IF stage t = 6? (1)

Assume first instruction is addi a0,zero,2

line6:beq a0,t1,choice2

### 65. How many cycles does this program take to complete? \_\_\_\_ (2)

20 cycles

## F. Pipeline CPU.

Consider the pipeline cpu above with the stage timings as shown below.

| MUX | ALU | DMEM | Regfile | IMMGEN | BRANCH | IMEM |

|-----|-----|------|---------|--------|--------|------|

|-----|-----|------|---------|--------|--------|------|

| MUX | ALU | DMEM | Regfile | IMMGEN | BRANCH | IMEM |

|-----|-----|------|---------|--------|--------|------|

| 20  | 220 | 230  | 100     | 30     | 30     | 200  |

# 66. Assuming that this CPU is NOT Pipelined (i.e. it is a singlecycle CPU), what is the

| shortest clock period possible to execute the instruction? |  |

|------------------------------------------------------------|--|

|                                                            |  |

| 200+100+220+20+230 = 770ps                                 |  |

## 67. Assuming that this CPU is Pipelined, what is the

shortest clock period possible to execute the instruction? \_\_\_\_\_

240ps